Desde o lançamento do Core 2 Duo em 2006, a AMD vem tendo dificuldades de companhar a Intel no high-end, limitando-se a manter uma briga de preços nos processadores mid-range e low-end, que são os mercados menos lucrativos, atacando com processadores com três e seis núcleos, usando clocks elevados e tudo o mais que tivesse à mão. Com o Sandy Bridge, a Intel avançou mais um degrau em termos de desempenho, demandando um contra-ataque da AMD na forma de uma nova arquitetura. Surgiu então o Bulldozer.

O Bulldozer é o sucessor do Barcelona (Phenom e Phemon II), destinado a ser usado nos processadores AMD da linha mainstream, deixando o low-end e os portáteis a cargo do Llano e do Brazos, bem como para os processadores remanescentes das linhas antigas. Ele é um processador com 4 módulos e 8 cores, produzido usando uma técnica de 32 nm com SOI e HKMG na Global Foundries. O Bulldozer é um chip colossal, com 1.2 bilhões de transistores e 315mm², bem maior que o Sandy Bridge, que embora também seja produzido em uma técnica de 32 nm, tem 995 milhões de transistores e mede apenas 216 mm². De fato, o Bulldozer é quase tão grande quanto o Thuban de 6 núcleos, que mesmo sendo produzido na antiga técnica de 45 nm, mede 346mm², apenas 31mm² a mais que o Bulldozer.

Apesar do tamanho, o Bulldozer não é uma APU como o Llano ou o Sandy Bridge, seguindo um design tradicional de CPU, incluindo apenas os processadores, caches, controlador de memória e PCI Express, deixando o vídeo por conta do chipset ou de uma GPU dedicada. Ele deu origem ao Zambezi, o processador destinado a desktops high-end, composto por quatro módulos Bulldozer:

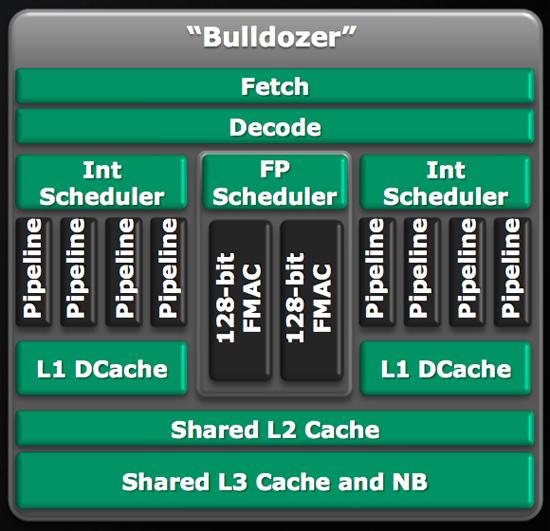

Pelo diagrama, você pode contar 4 módulos de processamento, cada um com um cache L2 de 2 MB, que são complementados por mais 8 MB de cache L3 (divididos em 4 módulos), compartilhados entre todos os módulos. À primeira vista, parece-se tratar de um processador quad-core com núcleos excepcionalmente grandes, mas na realidade cada módulo é composto por dois núcleos, que possuem caches L1, agendadores e unidades de execução independentes, mas que compartilham os estágios de fetch e decode e outros componentes, como se fossem gêmeos siameses:

Por outro lado, cada módulo possui um único agendador de operações de ponto flutuante, responsável pelas duas unidades de processamento de 128 bits com suporte a operações FMA (que agrupam operações de multiplicação em soma em uma única operação) e ao SSE 4. Essa disposição é a resposta da AMD ao HyperThreading da Intel, uma implementação “física” de uma arquitetura capaz de processar dois threads de cada vez, em oposição à abordagem da Intel, que é quase que puramente lógica. A desvantagem desta abordagem é que a AMD pagou um preço muito mais alto, já que a adição do segundo núcleo de processamento aumentou a contagem de transistores de cada módulo em cerca de 12%, contra os menos de 5% de aumento que temos no caso do HyperThreading nos processadores Intel.

Ao desenvolver a arquitetura do Bulldozer, a AMD se preocupou em melhorar o desempenho do processador em inteiros, com o desempenho em ponto flutuante e instruções SSE ficando em segundo plano, já que a ideia da AMD seria que os aplicativos fossem capazes de executar grande parte das operações de ponto flutuante usando a GPU. Em outras palavras, embora não tenha uma GPU integrada, o Bulldozer foi desenvolvido para servir como base para APUs de alto desempenho, que a AMD viria a lançar no futuro. Presumindo que a AMD ganhasse a queda de braço, convencendo os desenvolvedores a otimizarem seus aplicativos para o OpenCL, compartilhando a carga entre o processador e a GPU, essa combinação faria todo o sentido.

O grande problema é que o Bulldozer foi lançado sem uma GPU integrada e em um mundo em que a computação heterogênea (CPU+GPU) ainda está engatinhando. Isso fez com que a AMD acabasse com um design inadequado em mãos.

Deixe seu comentário