No início de 2006 a Intel estava em uma situação complicada. O Pentium D, baseado na ineficiente arquitetura NetBurst perdia para o Athlon X2 tanto em termos de desempenho quanto em termos de eficiência. Os processadores AMD eram superiores tanto nos desktops quanto nos servidores e a Intel perdia terreno rapidamente em ambas as frentes.

Quando tudo parecia perdido, a Intel apresentou a arquitetura Core, que deu origem as Core 2 Duo e aos demais processadores da linha atual. Para evitar cometer o mesmo erro que cometeu com a plataforma NetBurst, a Intel passou a investir massivamente em pesquisa e desenvolvimento, passando a desenvolver diversas novas arquiteturas em paralelo e a investir pesado no desenvolvimento de novas técnicas de fabricação e na modernização de suas fábricas.

O departamento de marketing se apressou em criar um termo que simboliza a nova fase, o “tick-tock” que passou a ser exaustivamente usado dentro do material publicitário da Intel. A idéia é bastante simples: apresentar novas arquiteturas e novas técnicas de fabricação em anos alternados, onde um “tick” corresponde ao lançamento de uma nova arquitetura (como o Penryn e o Nehalem) enquanto o “tock” corresponde ao lançamento de uma nova técnica de fabricação (45 nanômetros ou 32 nanômetros, por exemplo), fechando o ciclo. Ou seja, transformaram um conceito completo em uma idéia simples, acessível às massas.

O plano é manter o público interessado, anunciando uma nova arquitetura, ou a migração para um novo processo de fabricação uma vez a cada ano e manter um ritmo rápido de evolução, que a AMD tenha dificuldades para acompanhar. Dentro da idéia, a migração para a técnica de 0.065 mícron em 2005 foi um “tick”, o lançamento da plataforma Core, em 2006 foi um “tock” e o lançamento do Penryn em 2007, baseado na nova arquitetura de 0.045 mícron, foi um novo “tick”, que será seguido pelo lançamento de uma nova arquitetura (tock).

O Nehalem (pronuncia-se “nerreilem”) representa a próxima arquitetura Intel, ainda produzida usando a técnica de 45 nanômetros, mas com diversas mudanças arquiteturais em relação ao Penryn. As mudanças são tantas que podemos dizer que o Nehalem está para o Penryn assim como o Core 2 Duo está para o Pentium D; ou seja, trata-se realmente de uma nova arquitetura e não apenas de um Penryn com algumas melhorias.

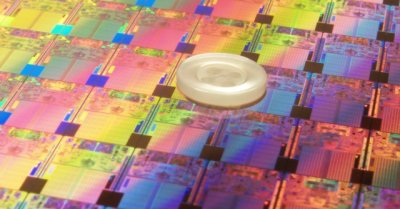

A versão inicial do Nehalem terá 4 núcleos, com um total de nada menos do que 781 milhões de transístores. Está prevista também uma versão com 8 núcleos, que terá provavelmente o dobro deste valor. Diferente de outros processadores quad-core da Intel, onde são usados dois dies separados (cada um com 2 núcleos), colocados dentro do mesmo encapsulamento e ligados através do FSB, o Nehalem quad-core é composto por um único die, ou seja, ele é um processador quad-core nativo.

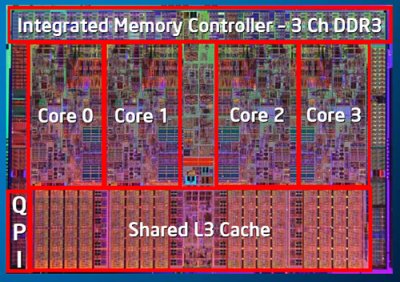

Uma das principais mudanças reside no sub-sistema de memória cache. O Nehalem mantém os mesmos 32 KB de cache L1 por núcleo usado no Penryn e em outros processadores anteriores, mas as similaridades param por aí. Em vez de um grande cache L2 compartilhado, a Intel optou por utilizar uma arquitetura similar à utilizada pela AMD no Phenom, com um pequeno cache L2 (de 256 KB) para cada núcleo e 8 MB de cache L3, compartilhado entre todos os núcleos.

A grande diferença reside na forma como os dados são armazenados nos caches. Nos processadores AMD é usado um cache “exclusivo”, onde o cache L2 armazena dados diferentes do cache L1 e o L3 armazena dados diferentes dos do L2, maximizando o espaço de armazenamento. A Intel, por outro lado, utiliza um sistema “inclusivo” onde os cache L1 e L2 armazenam cópias de dados também armazenados no cache L3.

Embora reduza o volume total de dados que pode ser armazenado nos caches, o sistema da Intel permite um acesso mais rápido aos dados armazenados. Em resumo, o sistema da AMD é mais eficiente em processadores com pouco cache, como no caso do Phenom, enquanto o sistema da Intel funciona melhor em processadores com grandes volumes de cache, como o Nehalem.

É nesse ponto que os investimentos da Intel em novas técnicas de produção se pagam, já que com transístores menores, eles podem se dar ao luxo de fabricar processadores maiores e com mais cache L2, mantendo o mesmo custo de produção das gerações anteriores.

A latência do cache L1 subiu de 3 para 4 ciclos em relação ao Penryn, mas em compensação a latência do cache L2 caiu consideravelmente, de 15 para 11 ciclos, de forma que o saldo final é positivo. O cache L3 trabalha com uma latência de 39 ciclos, o que pode parecer bastante se comparado com a latência dos caches L1 e L2, mas é um pouco mais rápido do que o cache L3 usado no Phenom, que trabalha com uma latência de 43 ciclos.

Outra mudança dramática é a inclusão de um controlador de memória integrado, assim como temos nos processadores AMD. O controlador de memória integrado reduz substancialmente o tempo de latência da memória, resultando em um ganho de desempenho considerável. Um dos grandes motivos o Athlon X2 ter se mantido competitivo em relação ao Core 2 Duo, apesar de possuir bem menos cache era justamente devido ao fato de utilizar o controlador dedicado.

A grosso modo, podemos dizer que o Athlon X2 precisa acessar a memória com mais freqüência (devido ao cache menor) mas que em compensação perde menos tempo a cada acesso devido ao controlador de memória integrado. A Intel bem que resistiu, mas acabou tendo que ceder à idéia.

Em vez de utilizar um controlador single-channel, ou dual-channel, a Intel optou por utilizar um controlador triple-channel, com suporte a memórias DDR3, operando a até 1.33 GT/s. Isso significa uma banda total de até 32 GB/s (ao utilizar 3 módulos). Para ter uma idéia, isso é 40 vezes mais do que tínhamos há 10 anos, quando utilizávamos módulos de memória SDR PC-100 em conjunto com o Pentium III.

Os três canais operam de forma independente, de forma que o processador por iniciar uma nova leitura em um dos módulos enquanto ainda espera os dados referentes a uma leitura anterior, realizada em outro módulo. Isso contribui para reduzir o tempo de latência do acesso à memória, que é, proporcionalmente, muito mais alto nos módulos DDR3.

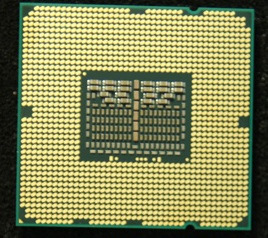

O problema com o controlador integrado é que ele aumenta substancialmente o número de contatos do processador, o que quebra completamente a compatibilidade com as placas soquete 775 atuais. A versão triple-channel do Nehalem utilizará um soquete LGA com nada menos do que 1366 contatos. O formato do processador também mudou, passando a ser retangular, assim como no antigo Pentium Pro:

Existirão também versões dual-channel, com apenas dois dos controladores de memória ativados, que possivelmente utilizarão um soquete menor, com um número menor de contatos.

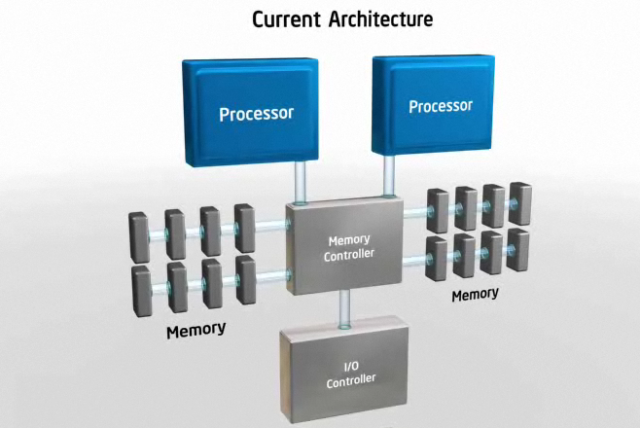

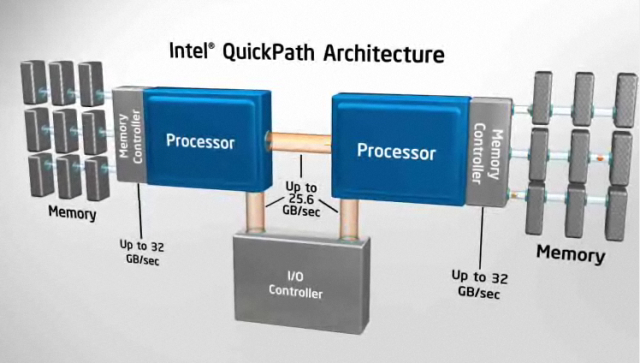

Outra mudança é a substituição do antigo FSB por um barramento aprimorado, batizado de QuickPath Interconnect, ou QPI. O FSB (front-side bus), ou barramento frontal, tem sido utilizado desde os primeiros processadores Intel. Ele consiste um um barramento compartilhado, que liga o processador ao chipset.

Como ele é usado não apenas para a comunicação entre os núcleos do processador e a memória, mas também para a comunicação entre os 2 ou 4 núcleos do processador, ele acaba estrangulando o acesso à memória, prejudicando o desempenho do sistema. O problema se agrava ao usar vários processadores em SMP, como no caso das placas para servidores, ou na plataforma Skultrail.

Até o Penryn a Intel remediou o problema na base da força-bruta, simplesmente adicionando mais cache L2 aos processadores. Com o QuickPath, resolveram atacar a raiz do problema, substituindo o FSB por um barramento modernizado, composto por links independentes que operam a 6.4 GT/s (a siga “GT/s” indica o volume de transações por segundo, diferente de “GHz”, que indica o clock), com a transmissão de 16 bits de dados em cada direção por ciclo, resultando em um barramento de 12.8 GB/s em cada direção (25.6 GB/s no total) por linha de dados. Como a memória é agora acessada diretamente pelo controlador de memória, este link fica inteiramente disponível para o tráfego de I/O. Ao utilizar dois processadores em SMP, cada processador passa a se comunicar com o chipset através de uma linha independente e uma terceira linha de dados é implantada para coordenar a comunicação entre os dois:

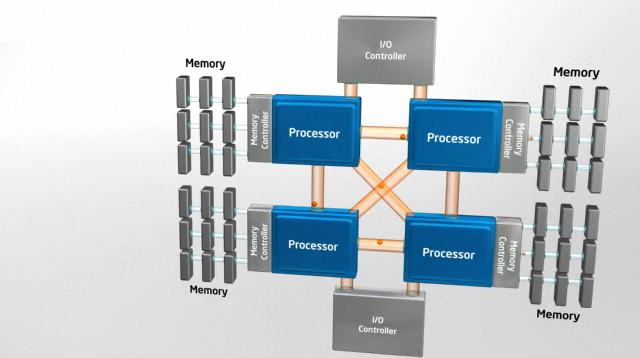

Ao usar 4 processadores (possibilidade que deverá ser bem explorada no caso dos servidores de alto desempenho) são incluídos barramentos adicionais, que fazem com que cada processador tenha acesso direto a todos os demais:

Se você leu meu tutorial sobre os processadores AMD de 64 bits, vai notar uma grande semelhança entre o QuickPath e o HyperTransport, usado nos processadores AMD. Obviamente, não se trata de mera coincidência. A Intel estudou os pontos fortes da solução da AMD e acabou chegando a uma solução melhorada, adaptada à sua arquitetura.

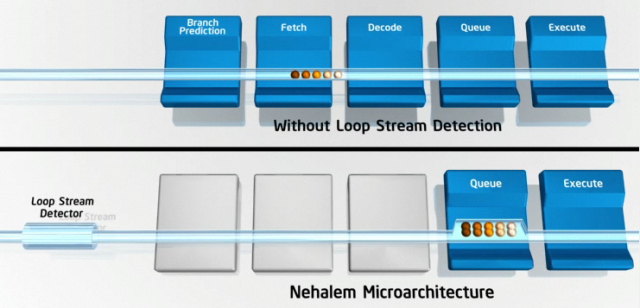

Com relação ao processamento das instruções, uma novidade importante é o Loop Stream Detector (LSD), um controlador adicional que vasculha as instruções decodificadas antes que elas cheguem ao processador, localizando instruções referentes a loops de processamento. Em vez de reprocessar as instruções do loop repetidamente, o processar armazena as instruções em um pequeno cache interno e as executa a partir daí. Além de permitir ganhar tempo, isso permite reduzir sutilmente o consumo elétrico, pois permite desativar o circuito de branch prediction, juntamente com as unidades fetch e decode durante o processamento do loop:

O Nehalem marca também a volta do Hyper Threading, o que faz com que o processador se apresente ao sistema operacional como tendo 8 núcleos em vez de 4. Naturalmente, o Hyper Threading não dobra o desempenho do processador, servindo apenas como um recurso extra que permite que ele aproveite melhor os recursos de processamento, processando dois threads simultaneamente sempre que possível.

Se você acompanhou a era do Pentium 4, talvez não tenha boas lembranças do Hyper Threading, já que ele reduzia o desempenho do processador em algumas operações e aumentava consideravelmente o consumo elétrico. A versão incluída no Nehalem, entretanto, passou por várias melhorias, sobretudo relacionadas ao consumo elétrico, de forma que podemos esperar uma redução significativa nos efeitos colaterais.

Ao contrário do deselegante Kentsfield (usado na primeira geração do Core 2 Quad), onde todos os núcleos operam sempre à mesma freqüência e usando a mesma tensão, o Nehalem oferece um sistema de gerenciamento independente, onde cada núcleo pode operar a uma freqüência condizente com seu nível de utilização, mantendo o consumo elétrico global do processador em níveis aceitáveis.

Graças à arquitetura modular usada no Nehalem, a Intel tem uma boa flexibilidade para desenvolver versões do processador com mais ou menos núcleos de acordo com a demanda. Além da versão com 4 núcleos, estão planejadas também versões com 2 e 8 núcleos.

O Nehalem já existe em versões limitadas, que estão sendo disponibilizadas a parceiros e fabricantes de placas-mãe. A Intel pretende lançar os primeiros processadores baseados no Nehalem em setembro, mas eles provavelmente estarão disponíveis em volume apenas a partir de outubro ou novembro. Para 2009, está prevista uma versão atualizada no Nehalem, o Westmere, que será produzida em uma técnica de 0.032 micron.

Para 2010 está prevista uma versão com uma GPU integrada, o Sandy Bridge. Existem dúvidas sobre o desempenho desta solução, já que a Intel não possui sequer um chipset 3D competitivo. Pode ser que se limitem a desenvolver uma versão atualizada do GMA3500 e integrá-lo ao processador para tirar proveito do controlador de memória integrado, mas pode ser também que apareçam com uma solução radicalmente diferente, como no caso do Larrabee. Por enquanto esta informação é guardada a sete chaves.

Combinando o novo sistema de cache com o controlador integrado de memória e as demais melhorias, ficou claro que a Intel estudou meticulosamente as vantagens arquiteturais introduzidas pela AMD nos últimos anos e elaborou cuidadosamente respostas para cada uma delas. Isso mostra como é benéfico ter dois fabricantes competitivos disputando o mercado. Sem a AMD, muito provavelmente ainda estaríamos presos à idade das trevas da arquitetura NetBurst. Grande parte da evolução nos processadores Intel que vimos de 2006 para cá se deve justamente à AMD.

A posição atual da AMD lembra um pouco a posição da Intel em 2006: acuada e tendo que competir com produtos superiores do concorrente com cortes de preço e soluções de valor agregado. Para piorar, a situação financeira da AMD também não anda boa, já que precisaram assumir dívidas para concretizar a compra da ATI, que agora estão tendo dificuldades para pagar devido à queda nas vendas. Mas, é nos momentos de dificuldade que surgem as melhores soluções (veja o caso da Intel). Esta é uma briga que ainda promete.

Deixe seu comentário