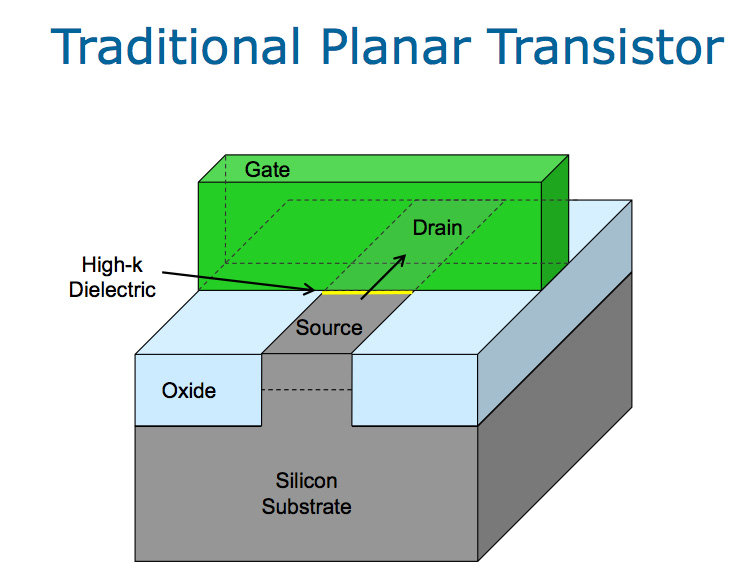

Apesar de todos os avanços, o projeto básico do transistor continua o mesmo desde a década de 60, uma estrutura plana, composta de basicamente três componentes: o emissor, coletor e a base, ou gate, que controla o fluxo de elétrons entre os dois pólos. Embora extremamente avançados, os transistores atuais continuam atuando como meras chaves digitais, com apenas dois estados, “1” e “0”. Colocando alguns bilhões deles nos lugares certos, juntamente com algumas células de memória SRAM e outros componentes, temos um processador moderno:

Uma fina camada abaixo do gate, chamada de inversion layer, é responsável por todo fluxo de elétrons, se comportando como um minúsculo fio entre os dois pólos de uma tomada. Na época em que os transistores mediam 180 nm ou mais, isso não era um problema, mas conforme eles foram encolhendo, o inversion layer foi se tornando cada vez mais fino e estreito, tornando-se menos eficiente. Com isso, cada vez mais energia flui entre o emissor e o coletor mesmo enquanto o transístor está desligado (o gate leakage) e menor é a diferença de tensão entre os dois estados.

Em vez de termos 1.0V (ou o equivalente à tensão nominal do processador) enquanto o transistor está ligado e 0V enquanto ele está desligado, temos tensões muito próximas nos dois estados, algo mais perto de 1.0V com ele ligado e 0.7V ou 0.8V com ele desligado, o que não apenas resulta em erros de processamento (obrigando os fabricantes a incluírem mais funções de checagem e redundância), quanto desperdiça muita energia, um problema que foi se acentuando com a introdução de cada novo processo de fabricação.

Tradicionalmente, este problema era atacado de duas formas: com a redução do gate leakage (através de tecnologias como o “high-k dielectric” e o “metal gate electrode”, HK/MG, que a Intel introduziu a partir dos 45nm) ou com o simples aumento na tensão, o que força a passagem de mais elétrons através do inversion layer, amenizando o problema da diferença das tensões, mas em compensação aumentando dramaticamente o gate leakage e o consumo elétrico. Como resultado, temos processadores que são capazes de operar com tensões muito baixas (baixo consumo) e processadores que são capazes de operar a frequências muito altas (desempenho), mas não as duas coisas ao mesmo tempo.

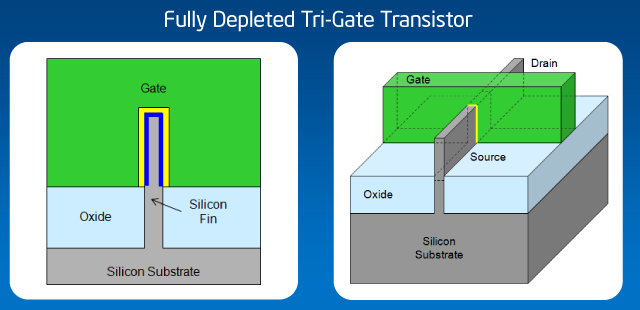

Com a chegada dos 22 nm essa questão se tornou ainda mais crítica, o que levou a Intel a apresentar uma solução alternativa para o problema: aumentar a área do inversion layer através da construção de uma estrutura tridimensional:

Esta é uma solução engenhosa, que representa uma mudança fundamental no projeto do transistor, resultando em uma área de contato muito maior e um melhor controle sobre o fluxo de elétrons. Como existem agora três pontos em que existe contato entre a inversion layer e o gate, os transistores baseados na nova tecnologia são chamados de “tri-gate”, muito embora a função lógica continue sendo a mesma, com um único gate fazendo contato em três faces. A Intel resolveu pegar carona na onda em torno do 3D para chamar o interesse do grande público, mas esta é apenas uma cartada de marketing.

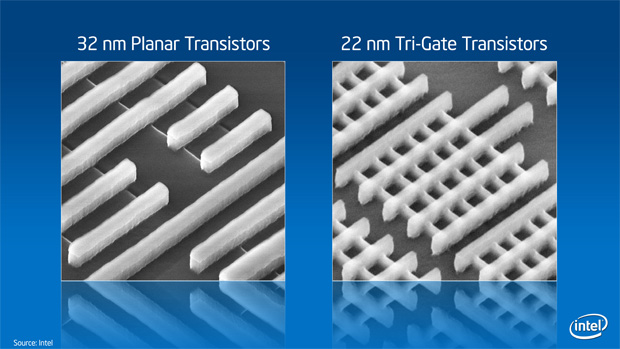

Para criar essa “protuberância” no gate os engenheiros foram forçados a introduzir várias etapas adicionais no já tedioso processo de aplicação de máscaras de litografia e banhos químicos empregado na fabricação (os detalhes estão sendo naturalmente guardados a sete chaves), mas o resultado final é realmente interessante. Aqui temos uma foto de divulgação da Intel que mostra transistores construídos usando a técnica convencional, a 32 nm, e os transistores tri-gate de 22 nm, que apresentam uma densidade muito maior:

Com uma área de contato tão maior, a diferença de tensão entre os estados “1” e “0” do transístor tornam-se muito maiores e o delay entre as mudanças de estado tornam-se menores. Isso permite que o transistor possa operar de forma confiável utilizando uma tensão mais baixa (menor consumo), ou que o processador opere a frequências mais altas mantendo uma tensão mediana e um consumo aceitável. Com isso, a Intel ganha uma vantagem técnica importante, que pode ser usada tanto para criar versões de baixo consumo do Atom (melhorando sua posição em relação aos chips ARM nos smartphones) quanto versões de alto desempenho de seus Core i5 e i7, fortalecendo sua posição no mercado high-end e mid-range.

Embora o processo de fabricação seja mais caro, por exigir o emprego de passos adicionais na produção, o ganho de eficiência permite espremer mais transistores no mesmo espaço, o que reduz a área do wafer ocupada por cada chip. Como o wafer é o componente mais caro, uma coisa acaba ajudando a compensar a outra. Segundo a Intel o aumento final no custo de produção é apenas 3%. O preço de venda por sua vez depende mais dos preços praticados pela concorrência, por isso não estão necessariamente relacionados.

Segundo a Intel, os novos transistores são capazes de chavear até 37% mais rápido que transistores regulares de 32 nm operando a 0.6V, ou até 18% mais rápido operando a 1.0V. O Atom, bem como os chips ULV se encaixam na primeira categoria, operando com tensões muito baixas, enquanto os chips para desktops se encaixam na segunda. Se os números da Intel realmente se materializarem na prática, poderemos ter chips móveis consumindo até 50% menos energia e chips para desktop operando com clocks até 18% mais altos, resultando em chips capazes de operar acima dos 5.0 GHz.

A tecnologia fará sua estreia com o lançamento do Ivy Bridge (esperado para o final de 2011) e será utilizada também em versões mais econômicas do Atom, destinadas a tablets e smartphones. Naturalmente, ainda precisaremos esperar até que os processadores cheguem ao mercado para avaliar os ganhos reais, mas não resta dúvidas de que este é um avanço importante.

O uso dos transistores tri-gate não é exatamente uma ideia nova. Ela foi originalmente proposta em 2002 por um engenheiro da Intel e tem sido discutida nos círculos técnicos desde então, com alguns convencidos da importância e viabilidade da tecnologia e outros descartando seu uso por considerá-la muito problemática. Praticamente todos os grandes fabricantes já realizaram testes com a tecnologia, mas a Intel acabou sendo a primeira a colocá-la em produção, em uma aposta que pode resultar em uma enorme vantagem competitiva (caso tudo dê certo) ou em atrasos e problemas caso surjam problemas durante a produção em grande escala dos chips. Outros fabricantes têm apostado no uso do SOI (Silicon on Insulator), uma tecnologia bem menos ambiciosa, mas em compensação já bem testada, que consiste no uso de uma fina camada isolante sob os transístores para reduzir o gate leakage.

É bem verdade que o tri-gate coloca uma pressão adicional sobre a AMD, que já estava sendo pressionada com o Sandy Bridge, mas não chega a representar uma ameaça existencial para a empresa, já que a AMD continua firme no mercado de GPUs, cuja importância só aumenta. Mesmo que a Intel eventualmente conseguisse dominar completamente o mercado de processadores, a AMD ainda continuaria bem viva vendendo suas GPUs e APUs.

Qualquer comprador interessado em um PC de alto desempenho vai querer também uma boa GPU, o que automaticamente o obriga a ir comprar com a AMD ou a nVidia. Com o Fusion a AMD conseguiu também uma posição confortável no mercado de netbooks e PCs de baixo-custo, onde a combinação do processador com uma GPU relativamente poderosa é bastante atrativa, independentemente de qualquer diferença no consumo elétrico.

Concluindo, os transistores tri-gate e a migração para a técnica de 22 nm são apenas mais um capítulo no avanço dos processadores. A Intel pretende manter o ritmo de introdução de uma nova técnica de produção a cada dois anos, aprontando a técnica de produção de 14 nm para 2013 e a de 10 nm para 2015.

Dez anos atrás, especulava-se que os 32 nm seriam o limite final para os chips de silício, mas a sequência de novas tecnologias esticaram este limite até os 10 nm, que podem finalmente ser o limite final. Quando ele for finalmente atingido, entraremos em uma nova fase, onde os ganhos introduzidos por novas técnicas de fabricação passarão a ser menores a cada geração e os fabricantes serão obrigados a investirem na otimização das arquiteturas.

Deixe seu comentário