A ideia de que o desempenho dos chips dobrará a cada 18 meses moldou o ramo da computação nas últimas décadas, permitindo que os fabricantes mantivessem os consumidores interessados, com sucessivas novas linhas de produtos que trouxessem ganhos tangíveis em relação às anteriores. Mesmo que não houvessem melhorias na arquitetura, a simples transição para uma técnica mais avançada de litografia era a garantia de clocks consideravelmente mais elevados e, como consequência, um desempenho muito superior. Dois exemplos são o Pentium III, que esbarrou nos 600 MHz com o Core Katmai (250 nm), mas chegou aos 1133 MHz com o Coppermine (180 nm) e aos 1.4 GHz com o Tualatin (130 nm) e o Pentium 4, que chegou aos 2.0 GHz com o Willamette (180 nm) e aos 3.4 GHz com o Northwood (130 nm) .

Assim como em todo lanche grátis entretanto, a Lei de Moore está prestes a acabar. De fato, é de se admirar que ela tenha durado tanto, indo do final da década de 1960 até bem depois da virada do milênio.

Uma década atrás, se teorizava que o processo de litografia poderia avançar apenas até os 30 nm e a partir daí a única saída seria migrar para os computadores quânticos, ou outro processo radicalmente diferente de produção. Neste meio tempo, novas tecnologias deram uma grande sobrevida ao uso da litografia. Não apenas já temos chips de 22 nm no mercado, como a geração seguinte, de 14 nm, já está em desenvolvimento, com a Intel planejando lançar chips de 10 nm no final de 2015:

Especula-se que seja possível estender o processo de litografia por mais uma geração depois dos 10 nm, mas a partir daí finalmente esbarraremos no limite fundamental do processo de litografia.

Mais do que uma simples questão de aquecimento, tensões ou de gate-leakage, desta vez o problema reside no próprio funcionamento dos transistores. Como bem sabemos, os transistores são baseados no uso de eletricidade para controlar o fluxo de elétrons entre os dois polos do transistor. No centro do transistor temos o gate, responsável por permitir ou bloquear o fluxo de elétrons de acordo com o estado lógico do transistor. Como qualquer barreira, o gate deixa de ser efetivo caso se torne muito estreito. Depois dos 10 nm, um fenômeno batizado de tunneling entra em cena, fazendo com que os elétrons possam passar aleatoriamente para o outro lado, mesmo que o gate não esteja ativo, fazendo com que o transistor deixe de ser confiável. Ao chegar aos 5 nm o problema se torna crônico e o salto passa a ocorrer em 50% das vezes, eliminando a possibilidade do uso de qualquer sistema de correção. Em uma escala tão pequena, o tunneling ocorre independentemente do material usado, o que elimina a possibilidade de que algum novo material possa estender o processo por mais gerações.

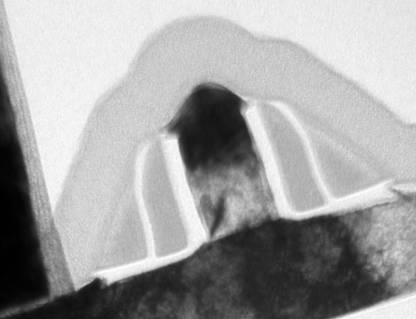

Na foto a seguir, temos uma imagem capturada com um microscópio eletrônico, mostrando o corte transversal de um transistor, com o gate no centro. Se fabricado usando uma técnica de 10 nm, o gate deste transistor teria apenas 10 átomos de espessura:

A partir daí, teremos um período de pelo menos uma ou duas décadas sem grandes revoluções, até que alguma nova arquitetura, baseada no uso de grafeno, nanotubos, engenharia molecular ou computadores quânticos se torne avançada e acessível o suficiente para ser produzida em escala. A viabilidade teórica de todas essas tecnologias já foi comprovada, mas existe uma grande diferença entre conseguir calcular o resultado de três vezes cinco usando um computador quântico de 5 qubits controlado através de uma máquina de ressonância magnética nuclear e um computador quântico funcional que possa ser colocado dentro de um chip e funcionar na temperatura ambiente, sem precisar de nenhum aparato especial.

Além da questão do limite físico para o processo de litografia, existe outro problema ainda mais imediato, que é o simples fato de novas técnicas de produção não estarem resultando em ganhos tangíveis de frequências de clock como antigamente, e em muitos casos tendo até mesmo o efeito oposto, como no caso do Ivy Bridge.

Em outras palavras, embora ainda tenhamos algumas gerações de miniaturização dos transistores de silício pela frente, o que reduzirá o custo de produção dos chips e permitirá a inclusão de mais componentes, mais caches e mais núcleos, a transição para os 22 nm deixou claro que os processos subsequentes não trarão mais ganhos consideráveis de clock como tivemos em gerações anteriores.

Continua sendo possível desenvolver chips capazes de atingir frequências de operação mais altas adicionando mais estágios de pipeline, como a Intel fez com o Pentium 4 ou como a AMD fez com o Bulldozer, mas o resultado final é que as perdas introduzidas pelo pipeline mais longo acabam superando os ganhos em grande parte dos casos, criando chips que além de quentes e gastadores, acabam não oferecendo um desempenho muito convincente. Outro problema é que a frequência de operação dos chips está cada vez mais restrita à dissipação térmica, fazendo com que frequências muito acima dos 4 ou 4.5 GHz demandem water-coolers ou soluções exóticas de resfriamento, que podem chegar a fazer algum sucesso entre os entusiastas, mas jamais chegarão ao mercado mainstream devido ao custo e à complexidade.

Em outras palavras, estamos entrando em uma era de avanços muito mais lentos em relação ao desempenho dos sistemas, especialmente em relação aos PCs, onde novos ganhos de desempenho serão mais centrados em melhorias na arquitetura e melhorias nos softwares (aproveitando melhor o poder computacional dos chips já existentes) e não em ganhos diretos de desempenho como antigamente.

Duas tendências nessa nova etapa são o melhor aproveitamento do poder computacional das GPUs (não é à toa que tanto a AMD quanto a Intel vêm investindo tão pesado no desenvolvimento das APUs) e na inclusão de mais decodificadores e processadores dedicados dentro dos chips, assim como no caso do Quick Sync, que usa um chip dedicado para a codificação dos vídeos.

O uso de componentes dedicados oferece uma grande vantagem sobre o uso de unidades programáveis tanto do ponto de vista do desempenho quanto do consumo elétrico, já que o hardware é desenvolvido de tal forma que processa os cálculos necessários diretamente, em vez de executar um software que por sua vez executa as operações. Um bom exemplo é que precisamos de um 486 DX-66 para decodificar um MP3 de 128 kbits, coisa que qualquer MP3-player xing-ling, com seu chip de 16 bits operando a 16 MHz ou menos consegue fazer por 10 horas ou mais usando uma única pilha AA.

Decodificadores dedicados são velhos conhecidos, usados desde o início da computação para a execução de tarefas como decodificação de áudio e video e processamento de sinais. É graças a eles que arquiteturas antigas, como o Amiga eram tão avançados em relação aos PCs da época em matéria de multimídia e que os smartphones e tablets ARM podem ser tão eficientes em relação ao consumo elétrico. O grande problema com os chips dedicados é que eles são macacos de um truque só, que são capazes de executar um único tipo de operação. Mude apenas sutilmente o formato de codificação dos vídeos por exemplo, e você precisará reverter para a velha decodificação via software.

Devido a isso, sempre teremos a convivência entre CPUs e chips dedicados. Entretanto, a tendência para o futuro é que as APUs e SoCs passem a incluir um número cada vez maior de circuitos dedicados para tarefas diversas, que ajudarão a melhorar o desempenho em diversas operações e ficarão desligados na maior parte do tempo, sem consumir energia.

Outro caminho para obter ganhos de desempenho é a otimização dos softwares, que também apresenta duas tendências. A primeira é a paralelização, o desenvolvimento de algoritmos capazes de dividir a carga de processamento em várias partes, de forma a tirar melhor proveito dos múltiplos núcleos encontrados nos processadores atuais e, principalmente, das centenas de unidades de processamento disponíveis nas GPUs. O segundo, sobre o qual poucos programadores gostam de falar a respeito é a otimização dos softwares para que eles façam o trabalho de forma mais eficiente, consumindo menos recursos de processamento. Esta tendência é mais percebida em softwares científicos no ambiente dos servidores, onde otimizar um pequeno bloco de código pode resultar economias tangíveis, mas é muito mais lento no ramo dos softwares domésticos, onde o enorme volume de linhas de códigos torna qualquer otimização manual inexequível devido ao brutal volume de horas de trabalho necessário.

Deixe seu comentário