Há poucos dias a AMD demonstrou pela primeira vez PCs utilizando seus novos processadores da linha Hammer. Na apresentação foram mostrados dois PCs, um rodando o SuSe Linux de 64 bits e o outro rodando o Windows XP de 32 bits, o que demonstrou a principal promessa do processador, a de rodar tanto aplicativos de 64 bits, quanto aplicativos de 32 bits, mantendo em ambos os casos um desempenho superior ao dos processadores de 32 bits atuais.

Para isso o Hammer utiliza uma arquitetura VLIW, que permite quebrar as instruções em blocos e processá-los de forma paralela. Isto adiciona a flexibilidade necessária para processar duas instruções de 32 bits como se fossem uma única instrução de 64 bits, sem (teoricamente) perda de performance. O Hammer possui dois modos de operação, o Legacy Mode e o Long Mode, onde são processadas respectivamente instruções de 32 e 64 bits. O processador pode chavear entre os dois modos muito rapidamente, o que permite rodar aplicativos das duas safras lado a lado, assim como os processadores atuais, que são capazes de rodar tanto código de 32 bits, quanto código de 16 bits.

A verdade é que no Hammer as instruções de 64 bits são implantadas como extensões. Todo o legado que vem desde o 8086 continua presente, o que aumenta bastante o número de transístores do chip em relação ao que seria necessário sem este fardo. O conjunto de instruções usado pela AMD chama-se x86-64 e é um padrão aberto para o uso de outros fabricantes, inclusive da Intel, que está apostando no seu IA-64, o conjunto de instruções de 64 bits utilizado no Itanium, infelizmente incompatível com o da AMD.

Esta primeira amostra do Hammer não acrescentou muitos detalhes, pois os processadores ainda fazem parte da série A0, ou seja, a primeira fornalha de processadores, produzidos com o objetivo de corrigir erros de projeto. Nem mesmo a frequência de operação dos processadores foi divulgada, a AMD se limitou a um vago “a uma frequência maior que os outros processadores de 64 disponíveis no mercado”, numa referência ao Itanium da Intel, que na versão mais rápida disponível hoje opera a 1.0 GHz. A primeira versão comercial do Hammer receberá o índice de desempenho 3400+, e operará a 2.0 GHz.

O sistema rodando o SuSe Linux tinha abertos lado a lado aplicativos de 32 bits e 64 bits, enquanto o com o XP rodava o Word e Excel:

Foto publicada pelo https://www.watch.impress.co.jp

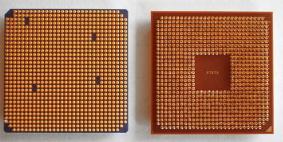

Foto publicada pelo https://www.watch.impress.co.jpExistirão duas versões do Hammer, o ClawHammer que será destinado a Workstations e PCs domésticos, e permitirá o uso de até dois processadores em SMP e o SledgeHammer, a versão mais cara, destinada a servidores, que permitirá o uso de até 8 processadores. A primeira coisa que chama a atenção em ambos os processadores é o número de pinos. O ClawHammer possui 754 pinos, enquanto o SledgeHammer exibe nada menos que 940 pinos, mais do dobro de um Athlon XP, que possui 462 pinos:

Foto publicada pelo https://www.tomshardware.com

Foto publicada pelo https://www.tomshardware.comEssa fartura de contatos deve-se ao controlador de memória incluído em ambas as versões do Hammer, que substitui o controlador incluído tradicionalmente no chipset. A vantagem neste caso é um ganho considerável na velocidade de acesso à memória, pois, incluído dentro do processador o controlador de memória pode operar na mesma frequência que ele e não a 100 ou 133 MHz junto com a placa mãe. Apesar dos pentes de memória continuarem operando na mesma frequência, a latência acaba sendo muito menor.

Ambos os chips utilizarão memória DDR PC-2700 (166 MHz) mas o ClawHammer utilizará um único pente, enquanto o SledgeHammer utilizará módulos aos pares, com um fabuloso barramento de 128 bits com a memória, similar ao usado no nForce.

É justamente por causa do barramento mais largo com a memória que o SledgeHammer possui mais pinos. Naturalmente o controlador de memória incluído no processador pode ser desabilitado e substituído por um controlador externo, caso surja alguma tecnologia de memória que se mostre superior às DDR, mas neste caso não existiria mais a vantagem de ter o controlador de memória operando na mesma frequência que o processador.

Um segundo componente incluído no processador é um controlador Hyper Transport, responsável pela comunicação com o chipset da placa mãe. Este é um diagrama publicado numa apresentação da AMD, que você pode ver aqui: https://www.amdzone.com/articleimages/conventions/idf/IDF%20Press%20Presentation%20VFINAL_files/frame.htm

O barramento Hyper Transport principal, entre o processador e a ponte norte do chipset tem 16 bits de largura e opera a 1.6 GHz, resultando num barramento de dados de 6.4 GB/s (sentido único. No sentido inverso, ou seja, do chipset para o processador temos um barramento um pouco mais estreito, com 8 bits e 3.2 GB/s ou 16.6 GB/s, dependendo do chipset usado (AMD 8131 ou AMD 8351). O barramento secundário entre a porte norte e a ponte sul do chipset possui 8 bits de largura, a 800 MHz resultando num barramento de dados de 800 MB/s em cada sentido, o suficiente para abrigar folga slots PCI de 32 bits, portas USB, ATA 100, ACR, etc.

Este outro slide mostra uma implementação do SledgeHammer em conjunto um chipset da série 8000 da AMD, num sistema quad-processor:

Veja que apesar da placa continuar tendo apenas um chipset, cada processador dispõe de um barramento de memória exclusivo, o que é um dos grande trunfos da AMD contra os Xeons e Itaniuns da Intel, onde todos os processadores compartilham o mesmo barramento com a memória RAM.

Claro que esta solução também tem seus pontos fracos, pois além de aumentar o número de pentes de memória necessários, faz com que os dados se repitam na memória controlada por cada processador. Além disso, passa a ser necessário um sistema bastante complexo de verificação para detectar qual processador possui os dados mais recentes em cada situação e transferí-los para o processador que precisar deles para concluir uma operação qualquer. Além de aumentar a complexidade (e o custo) da placa mãe, esta solução também causa teoricamente, uma pequena diminuição na performance. Ou seja, é preciso pesar na balança o ganho de desempenho com os barramento exclusivos com a perda causada pela constante checagem dos dados.

O Hammer não será um processador destinado a atingir frequências de operação tão altas quanto o Pentium 4, pelo contrário, ele possui os mesmos 12 estágios de pipeline que o Athlon (contra 20 estágios do Pentium 4). Isto significa que o processador será capaz de processar mais instruções por ciclo, graças a todas as melhorias, mas em compensação não será capaz de atingir frequências de operação muito altas.

Se o Hammer de 2.0 GHz receberá o índice 3400+, significa que o desempenho por clock será cerca de 26% superior ao de um Athlon XP (pelo menos segundo as contas da AMD) já que um Athlon XP 3400+ deveria operar a aproximadamente 2.8 GHz.

Segundo o último RoadMap da AMD a primeira versão do ClawHammer, sem suporte a SMP será lançada entre o final de 2002 e o início de 2003, seguida pelas versões do ClawHammer com suporte a SMP e das primeiras versões do SledgeHammer, que serão lançadas durante o primeiro semestre de 2002. Toda esta primeira safra será fabricada numa técnica de 0.13 mícron, com SOI, na mesma fábrica usada para a produção dos processadores Athlon com core Barton (o sucessor do Thoroughbred produzido atualmente), mas no segundo semestre de 2003 o ClawHammer passará a ser produzido numa técnica de 0.09 mícron.

Mais uma novidade é que todos os processadores da série Hammer utilizarão um dissipador metálico, uma proteção contra danos mecânicos, semelhante ao usado no Pentium 4:

Fotos publicadas pelo https://www.watch.impress.co.jp

Fotos publicadas pelo https://www.watch.impress.co.jp

Esta proteção é necessária, pois o Hammer terá mais que o dobro de transístores que o Athlon, o que significa mais que o dobro de calor por ciclo de clock. Isto nos obrigará a usar coolers muito grandes e pesados (principalmente no caso dos de cobre) nas versões mais rápidas do Hammer, que poderiam quebrar facilmente o core caso ele ficasse exposto como no caso do Athlon.

Os processadores da apresentação rodavam sobre um protótipo de placa mãe desenvolvido pela AMD, batizada de Solo 2. Esta placa não traz nenhum recurso muito especial, de incomum temos apenas o suporte a USB 2.0 (os três conectores coloridos ao lado da porta da impressora) e o conector ATX12V, como os usados pelo Pentium 4, que adiciona o pré-requisito de uma fonte de alimentação com o conector extra:

Foto publicada pelo https://www.tomshardwareguide.com

Foto publicada pelo https://www.tomshardwareguide.comFalta agora esperar o lançamento dos processadores, para que finalmente possamos ver como ficará o desempenho. A migração dos aplicativos de 32 para 64 bits será gradual, assim como até hoje ainda usamos muitos programas de 16 bits, apesar do 386 ter sido lançado em 85. Ou seja, para um usuário doméstico não haverá nenhuma urgência em migrar.

Por outro lado, além dos servidores de banco de dados os aplicativos de edição de vídeo e multimídia em geral poderão ter ganhos consideráveis de desempenho graças à arquitetura de 64 bits. Aplicativos especializados, como o 3D Studio, Photoshop, etc. serão os primeiros a ganhar versões de 64 bits e até lá o Windows de 64 bits também estará pronto. No caso dos aplicativos Linux a migração será mais fácil, pois bastará recompilar os programas utilizando o compilador compatível com as instruções do Hammer que já está disponível. Isto pode ser feito tanto pelo desenvolvedor ou distribuidor do programa quanto pelos próprios usuários, pelo menos no caso dos aplicativos de código aberto.