Depois de falar sobre os aparelhos e sobre a evolução dos sistemas operacionais, falta falar mais sobre a evolução da arquitetura dos chips ARM, bem como dos SoCs, que são o coração que qualquer smartphone ou tablet que você possa encontrar no mercado. O nível de integração obtido nos SoCs atuais é um verdadeiro milagre da engenharia por seu próprio mérito e é a chave para a eficiência energética dos aparelhos atuais. Ela é também o principal motivo de a Intel ter demorado tanto tempo para conseguir entrar no mercado móvel, já que embora tivesse o Atom já há vários anos, só recentemente foram capazes de integrar os demais componentes, criando um SoC competitivo, como o Medfield. Vamos a eles:

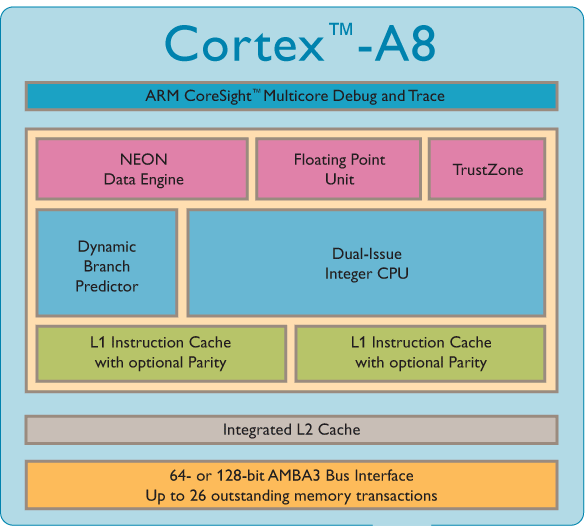

Se o ARM11 é similar ao 486 em arquitetura, oferecendo uma única unidade de execução, com o processamento de instruções em ordem, o Cortex A8 lembra um pouco a arquitetura do Pentium, sendo um processador dual-issue (duas unidades de execução), que processa instruções em ordem (assim como o Intel Atom) e inclui um cache L1 de 64 KB, dividido em dois blocos de 32 KB (dados e instruções). Ele inclui também um grande (do ponto de vista de um chip para sistemas embarcados) cache L2 de 256 KB, que pode ser expandido para até 1 MB de acordo com o nível de desempenho desejado pelo fabricante.

Na verdade (assim como outros chips ARM), o Cortex A8 é apenas um projeto de chip, que é licenciado pela ARM pra diferentes fabricantes, que se encarregam da produção e têm liberdade para realizar mudanças no projeto, incluindo desde pequenas modificações, como uma quantidade maior de cache L2, por exemplo, até modificações mais profundas na forma como o processador executa instruções, o que acaba levando a diferenças de desempenho nos diferentes SoCs equipados com o mesmo chip. Alguns fabricantes, como a nVidia e a Texas Instruments costumam preservar o projeto básico do chip, tentando diferenciar seus SoCs com base no chipset de vídeo e outros componentes integrados, enquanto outros, como a Samsung e a Qualcomm são mais ávidos por implantar modificações nos chips que possam oferecer algum benefício competitivo. Em geral essas modificações resultam em ganhos pequenos de desempenho, na casa dos 3 a 10%, com o desempenho bruto continuando a depender mais da frequência de clock e dos caches.

O Cortex A8 incorporou também um pipeline de 13 estágios (contra os 8 estágios do ARM11), o que possibilita o uso de frequências de operação muito mais altas. Os primeiros SoCs baseados nele foram produzidos usando uma técnica de 65 nm (como os usados no iPhone 3GS e no Nokia N900, bem como o do Milestone original) e operavam na casa dos 600 MHz, mas estes chips suportam bons overclocks, podendo em muitos casos operar estavelmente a 1.0 GHz ou mais, como no caso do TI OMAP 3430, usado no Milestone. Entretanto, a frequências tão altas o consumo do chip cresce bastante, comprometendo a autonomia da bateria. Assim como temos no caso dos chips ULV para notebooks, a frequência de operação dos SoCs ARM é geralmente limitada pelo envelope de consumo desejado pela fabricante, e não pelo que o chips realmente podem oferecer.

A grande vantagem do Cortex A8 sobre o ARM11 é o desempenho. Além de oferecer um desempenho bruto por clock duas vezes superior (até 2 DMIPS por MHz, contra apenas 1 a 1.1 DMIPS por MHz no ARM 11), ele é capaz de operar a frequências mais altas, o que faz com que o desempenho da maioria dos SOCs seja pelo menos duas vezes superior ao dos chips da geração anterior. O Cortex A8 inclui também um coprocessador aritmético, o VFPv3 (embora o uso por parte dos fabricantes não seja obrigatório) e suporte ao NEON, um conjunto de instruções SIMD nos mesmos moldes do 3D-Now e do SSE.

A grosso modo, poderíamos comparar o ARM11 com o 486 (que processava uma instrução por ciclo e estacionou na casa dos 100 MHz) e o Cortex A8 com o Pentium (que processava duas instruções por ciclo e chegou aos 200 MHz). É possível também traçar um paralelo com o Atom, que (sendo baseado na arquitetura do Pentium 1) também processa duas instruções por ciclo e também usa um pipeline relativamente curto (para um processador x86), com 16 estágios.

Deixe seu comentário